# Modélisation de Systèmes Numériques Intégrés Introduction à VHDL

Alain Vachoux

Xemics S.A.

alain.vachoux@xemics.ch

# Table des matières

| 1. Introduction                                                          | 7  |

|--------------------------------------------------------------------------|----|

| 1.1. Notion de modèle                                                    | 9  |

| 1.2. Représentation de la conception                                     | 11 |

| 1.3. Langage de description de matériel                                  | 13 |

| 1.4. Exemple de description comportementale, structurelle et géométrique |    |

| 1.5. Simulation logique                                                  | 17 |

| 1.6. Synthèse logique                                                    |    |

| 100.25 miles 10g.que                                                     |    |

| 2. VHDL                                                                  | 21 |

| 2.1. Flot de conception basé sur VHDL                                    | 23 |

| 2.2. Environnement de travail VHDL                                       | 25 |

| 2.3. Modèle sémantique de VHDL                                           | 27 |

| 2.4. Organisation d'un modèle VHDL                                       |    |

| Unités de conception                                                     |    |

| Entité de conception                                                     | 29 |

| 2.5. Modèles VHDL d'un registre 4 bits                                   | 31 |

| Déclaration d'entité                                                     |    |

| Architecture comportementale                                             |    |

| Architecture structurelle                                                |    |

| Environnement de test                                                    |    |

| Instanciation directe                                                    |    |

| Spécification de configuration                                           |    |

| Remarque                                                                 |    |

| 2.6. Modèles génériques                                                  | 41 |

| Paramètres génériques                                                    | 41 |

| Objets d'interface non contraints                                        |    |

| Instruction generate                                                     |    |

| 2.7. Concurrence et modélisation du temps                                |    |

| Processus et signaux                                                     |    |

| Initialisation et cycle de simulation                                    |    |

| Délai inertiel                                                           |    |

| Délai transport                                                          |    |

| Transactions multiples                                                   |    |

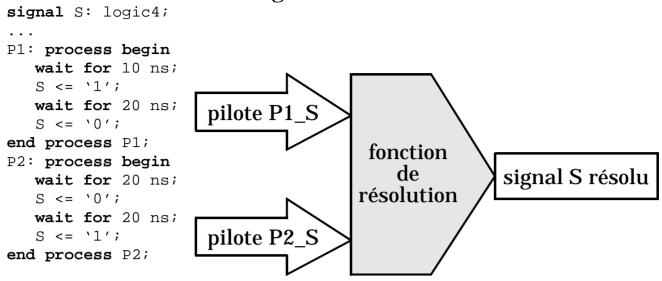

| Signaux résolus                                                          | 57 |

| 2.8. VHDL pour la synthèse                                               |    |

| Types (et sous-types) supportés                                          |    |

| Objets supportés                                                         |    |

| Valeurs initiales                                                        |    |

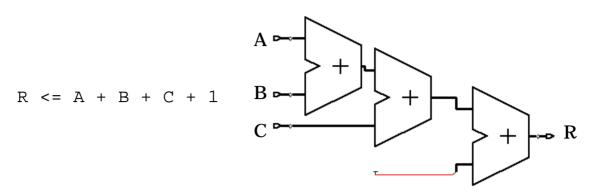

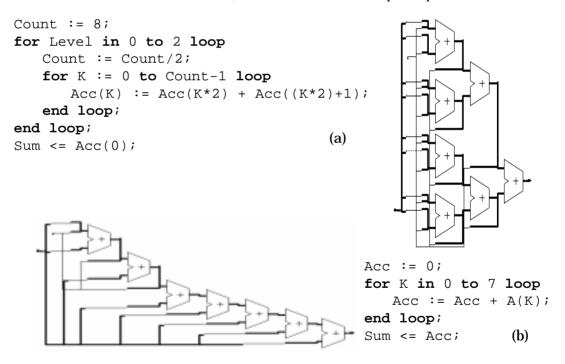

| Groupement d'opérateurs                                                  |    |

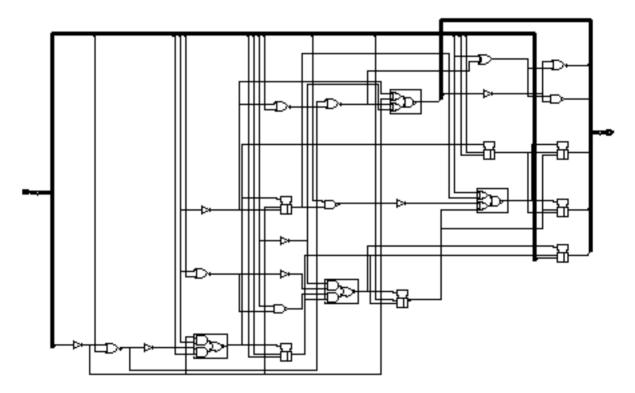

| Partage de ressources                                                    |    |

| Utilisation de processus et de l'instruction wait                        |    |

| Instructions séquentielles supportées                                    |    |

| Instructions concurrentes supportées                           |      |

|----------------------------------------------------------------|------|

| Paramètres génériques                                          |      |

| 3. Modélisation de circuits numériques                         | 81   |

| 3.1. Circuits logiques combinatoires                           |      |

|                                                                |      |

| Equations logiques                                             |      |

| Encodeurs                                                      |      |

| Décodeurs                                                      |      |

| Comparateurs                                                   |      |

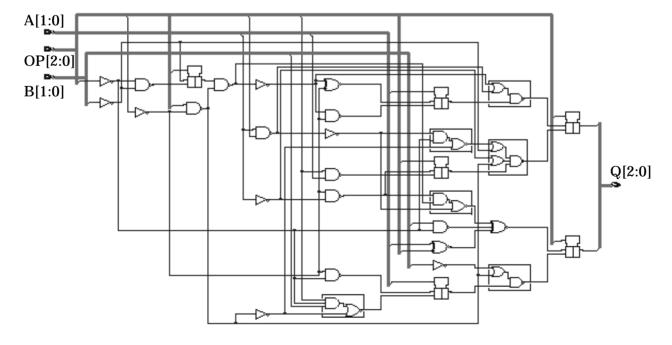

| Unité arithmétique et logique (ALU)                            |      |

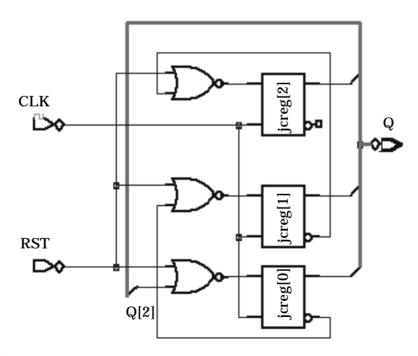

| 3.2. Circuits logiques séquentiels                             | 95   |

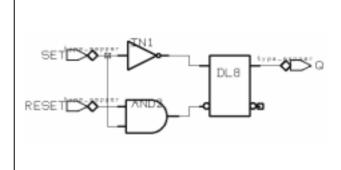

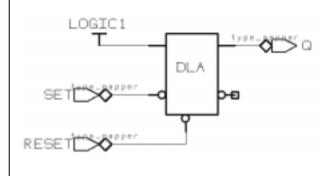

| Latches                                                        |      |

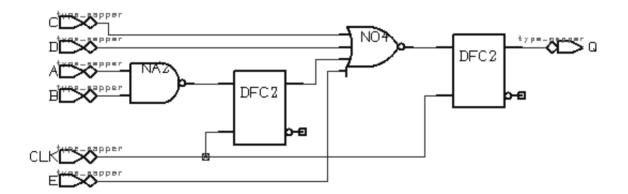

| Flip-flops                                                     |      |

| Registres                                                      |      |

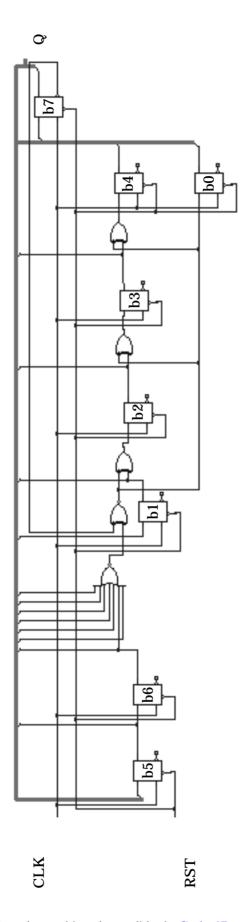

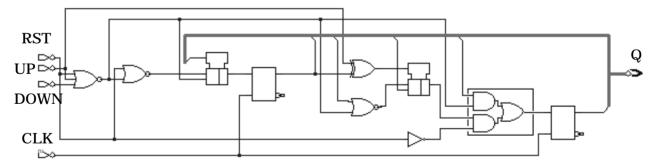

| Compteurs                                                      | 103  |

| 3.3. Circuits avec état haute-impédance                        | 105  |

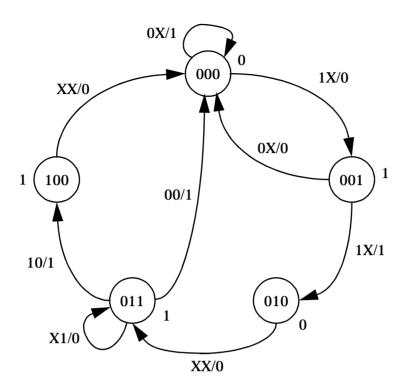

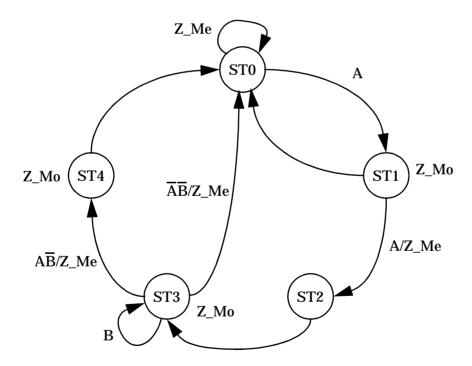

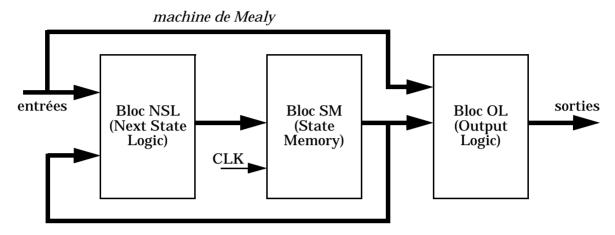

| 3.4. Machines à états finis                                    | 111  |

| Table des états et diagramme d'états                           | 111  |

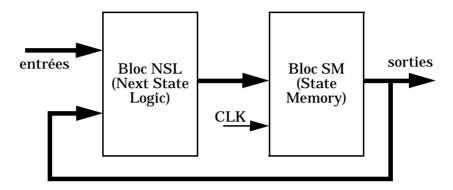

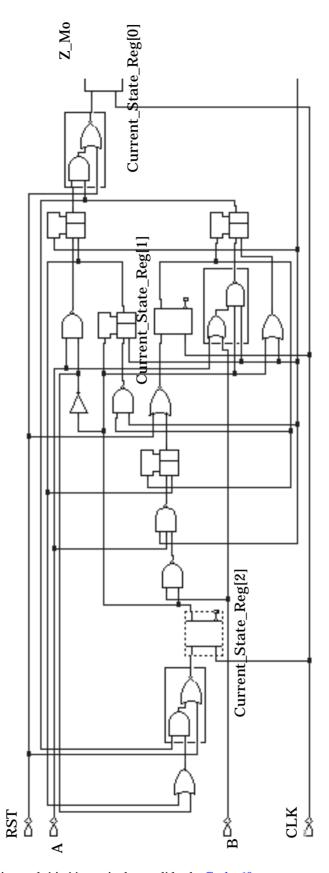

| Structure d'une machine à états finis                          |      |

| Modélisation avec un processus et registre d'état explicite    |      |

| Modélisation avec trois processus et registre d'état explicite |      |

| Modélisation avec registre d'état implicite                    |      |

| Reset synchrone/asynchrone et comportement sain                |      |

| Encodage des états                                             |      |

| Variantes possibles de machines d'états                        |      |

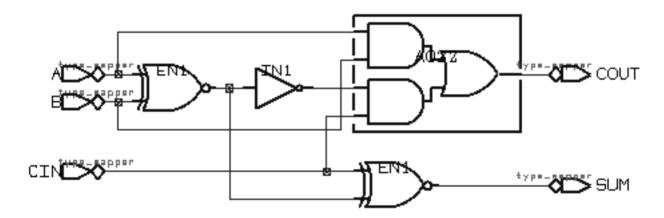

| 3.5. Opérateurs arithmétiques                                  |      |

| Additionneurs/Soustracteurs                                    |      |

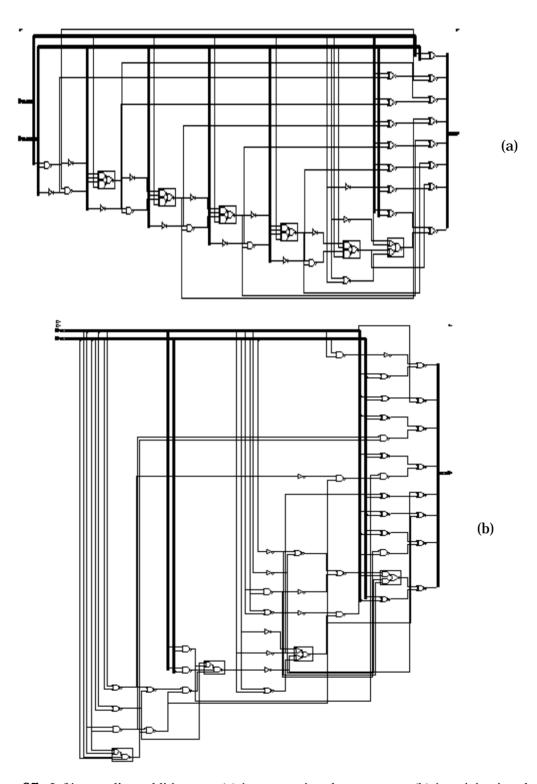

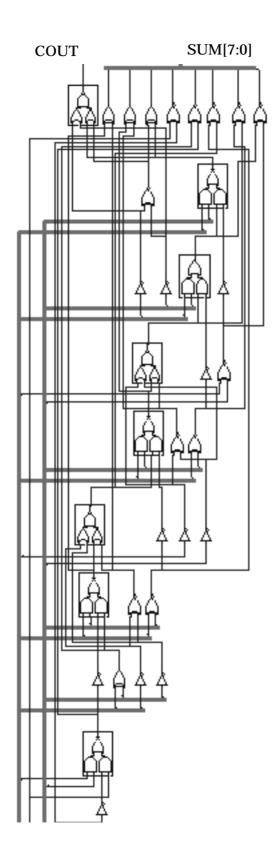

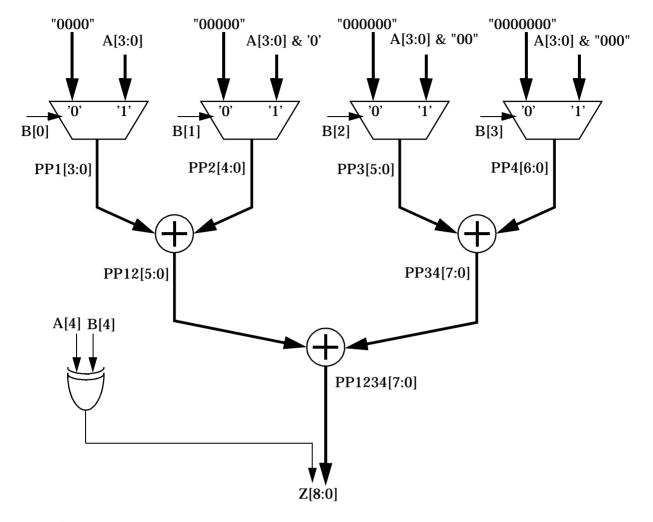

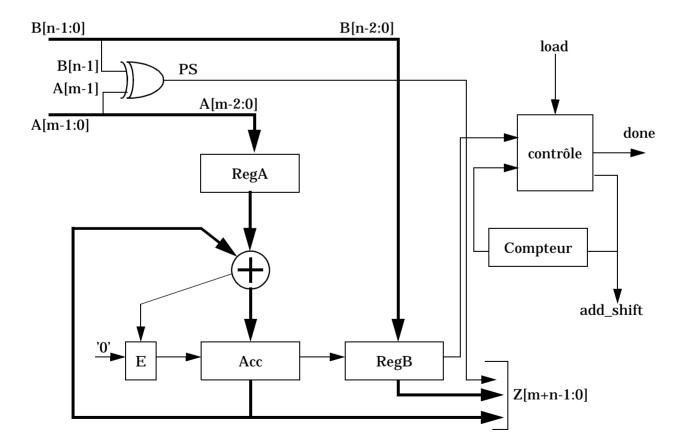

| Multiplieurs                                                   |      |

| 1                                                              |      |

| Annexe A: Syntaxe VHDL                                         | A-1  |

| A.1. Format de description de la syntaxe                       |      |

| A.2. Eléments de base                                          | A-1  |

| A.2.1 Identificateurs et mots réservés                         | A-1  |

| A.2.2 Litéraux caractère                                       |      |

| A.2.3 Litéraux chaînes de caractères et chaînes de bits        |      |

| A.2.4 Litéraux numériques                                      |      |

| A.2.5 Agrégats                                                 |      |

| A.2.6 Commentaires                                             | A-4  |

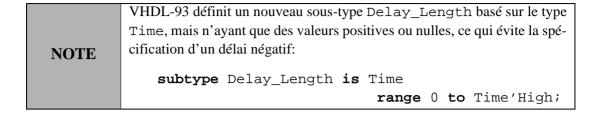

| A.2.7 Types et sous-types                                      | A-5  |

| Types numériques                                               | A-5  |

| Types énumérés                                                 | A-6  |

| Types physiques                                                | A-6  |

| Types tableaux                                                 |      |

| Types enregistrements                                          |      |

| Types accès                                                    |      |

| Types fichiers                                                 |      |

| A.2.8 Objets                                                   |      |

| Constantes                                                     |      |

| Variables                                                      |      |

| Fichiers                                                       | A-10 |

| Signaux                                                           |      |

|-------------------------------------------------------------------|------|

| A.2.9 Attributs                                                   |      |

| A.2.10 Alias                                                      |      |

| A.2.11 Expressions et opérateurs                                  |      |

| A.3. Unités de conception                                         |      |

| A.3.1 Clause de contexte                                          | A-16 |

| A.3.2 Déclaration d'entité                                        |      |

| A.3.3 Corps d'architecture                                        |      |

| A.3.4 Déclaration de paquetage                                    |      |

| A.3.5 Corps de paquetage                                          |      |

| A.3.6 Déclaration de configuration                                |      |

| A.3.7 Déclarations d'interfaces                                   |      |

| A.3.8 Déclaration de composant                                    |      |

| A.3.9 Association                                                 |      |

| A.4. Instructions concurrentes                                    |      |

| A.4.1 Processus                                                   |      |

| A.4.2 Assignation concurrente de signal                           |      |

| Assignation concurrente simple                                    |      |

| Assignation concurrente conditionnelle                            |      |

| Assignation concurrente sélective                                 |      |

| A.4.3 Instance de composant                                       |      |

| A.4.4 Génération d'instructions                                   |      |

| A.5. Instructions séquentielles                                   |      |

| A.5.1 Assignation de signal                                       |      |

| A.5.2 Assignation de variable                                     |      |

| A.5.3 Instruction conditionnelle                                  |      |

| A.5.4 Instruction sélective                                       |      |

| A.5.5 Instructions de boucle                                      |      |

| A.5.6 Instruction wait                                            |      |

| A.6. Sous-programmes                                              |      |

| A.6.1 Procédure                                                   |      |

| A.6.2 Fonction                                                    |      |

| A.6.3 Surcharge                                                   |      |

| A.6.4 Sous-programmes dans un paquetage                           |      |

| Annexe B: Paquetages VHDL standard                                | B-1  |

| B.1. Paquetage STANDARD                                           | B-1  |

| B.2. Paquetage TEXTIO                                             |      |

| B.3. Paquetage STD_LOGIC_1164                                     |      |

| B.S. Fuqueunge STB_EO CIC_110 · · · · · · · · · · · · · · · · · · |      |

| Annexe C: Autres paquetages VHDL                                  |      |

| C.1. Paquetage STD_LOGIC_ARITH                                    |      |

| Annexe D: LFSR                                                    | D-1  |

|                                                                   |      |

| Références                                                        | R-1  |

#### 1. Introduction

L'évolution constante des techniques de fabrication permet d'envisager la conception de systèmes matériels (hardware systems) de plus en plus complexes. Un système qui occupait il y a peu une ou plusieurs cartes (circuits imprimés, printed circuit board (PCB)) peut désormais tenir sur une seule puce de silicium (circuit intégré, integrated circuit (IC)). Le processus de conception doit donc faire face à une quantité croissante d'informations devenant elles-mêmes plus complexes. D'un autre côté, le marché impose un temps de conception (et de fabrication) le plus court possible de manière à réagir rapidement à la demande. Ceci impose dès lors un certain nombre de contraintes sur le cycle de conception:

- Une exploration efficace de l'espace des solutions. Il s'agit de prendre les bonnes décisions le plus tôt possible.

- Une réutilisation optimum de l'expertise acquise. Il s'agit déviter de repartir systématiquement de zéro à chaque fois.

- La possibilité de changer facilement de style de conception (design style) et/ou de technologie tout en garantissant une nouvelle version optimisée du système. Par exemple, une réalisation sur FPGA (Field Programmable Gate Array) peut consituer la version prototype, alors que la version finale sera réalisée sous la forme d'un ASIC (Application Specific Integrated Circuit).

L'utilisation d'outils logiciels d'aide à la conception devient ainsi essentielle pour satisfaire les contraintes cidessus, principalement grâce à leur faculté de traiter un très grand nombre d'information et d'automatiser certaines tâches de routine ou répétitives. Parmi ceux-ci, les outils EDA (*Electronic Design Automation*) tentent plus particulièrement de prendre en charge des activités de synthèse pour lesquelles le concepteur fournit une description relativement abstraite des spécifications du système (comportement désiré et contraintes à satisfaire) et laisse l'outil lui proposer des solutions sous la forme de structures possibles (architectures, schéma logique, schéma électrique, *layout*). La validation des descriptions initiales et des solutions trouvées se fait alors par simulation ou par preuve formelle.

Le processus de conception passe ainsi par un certain nombre d'étapes, chacune d'elles nécessitant une description de l'état du système sous forme graphique (diagrammes, schémas, etc.) ou textuelle (algorithmes, liste de pièces et connectivité (*netlist*), etc.). Ces descriptions peuvent être fournies par le concepteur ou produites par des outils logiciels. On peut distinguer deux types de descriptions:

- Les descriptions qui ne sont destinées à être lues et comprises que par des outils logiciels. On parle dans ce cas de *formats d'échange* (*interchange format*). On trouve par exemple dans cette catégorie les formats CIF et GDSII pour le layout et EDIF pour le schéma et le layout.

- La seconde famille regroupe les descriptions destinées à être en plus lues et comprises par des concepteurs. On parle alors de *langages de description de matériel* (hardware description language, HDL) et le langage VHDL en est un exemple.

#### Notion de modèle

- Support pour:

- Analyse: extraction de propriétés

- Synthèse: dérivation d'une description plus détaillée et éventuellement optimisée

- Nécessité d'un modèle:

- Manque d'information

- Surplus d'information

- Mode de fonctionnement d'un système matériel:

- Logique, dirigé par événements

- Analogique, continu

- Mixte

- Technique de modélisation:

- Discrète

- Continue

- Mixte

#### 1.1. Notion de modèle

La modélisation est une activité essentielle dans le processus de conception d'un système matériel, car elle est à la fois le support pour l'analyse et la synthèse.

L'analyse d'un système matériel consiste à extraire un certain nombre de propriétés à partir d'une description du système. L'analyse peut être faite par simulation, c'est-à-dire que la description est soumise à un ensemble de stimulis et le programme de simulation calcule l'état résultant du modèle (p. ex. une simulation logique temporelle). L'analyse peut aussi être faite par examen des propriétés du système sans qu'il soit nécessaire de lui appliquer des stimulis (p. ex. le calcul des délais des chemins d'entrée-sortie ou la vérification qu'une connexion de transistors ne possède pas de court-circuits ou de noeuds non connectés).

La *synthèse* d'un système matériel consiste à transformer une description de départ en une nouvelle description plus détaillée et éventuellement optimisée pour tenir compte de contraintes imposées (p. ex. surface minimum, délais minimum). Par exemple, partir d'un algorithme décrivant la fonction du système et en dériver un circuit logique capable de réaliser cette fonction tout en garantissant un temps de propagation donné.

Un modèle est une description abstraite d'un ensemble de phénomènes physiques: seuls les paramètres nécessaires à la tâche d'analyse ou de synthèse sont pris en compte. La nécessité de travailler avec une description abstraite peut s'expliquer par deux raisons mutuellement exclusives:

- *Manque d'information*: le système est en cours de conception et tous ses paramètres ne sont pas encore connus. Par exemple, l'algorithme d'une fonction à réaliser définit à la fois la séquence des opérations et les opérations elles-mêmes à effectuer, mais pas l'architecture du circuit ou le circuit lui-même qui réalisera la fonction donnée.

- Surplus d'information: l'analyse d'un système peut devenir fastidieuse, voire impossible, si la description est trop complexe. Il n'est par exemple pas réaliste d'analyser le comportement d'un microprocesseur si ce dernier est décrit au niveau des portes logiques et des transistors qui le composent et s'il ne s'agit que de vérifier son jeu d'instructions.

Un système matériel est usuellement caractérisé comme ayant un fonctionnement *logique* (*digital*) ou *analogique*. Un fonctionnement logique, ou discret, est défini par un nombre fini d'états possibles et d'actions (événements, *event-driven behaviour*) qui permettent d'atteindre ces états. Les états sont des grandeurs logiques (quantifiées) ou continues seulement définies à des instants particuliers. Un fonctionnement analogique, ou continu, est défini par un ensemble fini d'équations (différentielles, algébriques, linéaires ou non-linéaires) dont la solution est un ensemble de formes d'ondes (*waveforms*) continues fonction d'une variable indépendante (le temps ou la fréquence). Un système matériel peut également exhiber un comportement mixte logique-analogique.

La technique de modélisation peut être quant-à-elle discrète ou continue, ou un mélange des deux, selon le genre d'information que l'on désire obtenir par l'analyse et ceci indépendemment du mode de fonctionnement logique ou analogique du système modélisé. Par exemple, il est concevable d'analyser un circuit logique en considérant sa description équivalente au niveau du transistor pour en extraire des valeurs précises de délais. Il est aussi concevable de décrire le comportement d'un comparateur analogique comme un modèle à deux états dirigé par un événement qui est le changement de tension à l'entrée. Il est finalement naturel de décrire le comportement d'un convertisseur analogique-logique ou logique-analogique comme une combinaison de fonctionnements dirigés par événements et continus. Le choix de la bonne technique de modélisation est aussi conditionné par les algorithmes mis en oeuvre par le simulateur utilisé.

# Représentation de la conception

| Niveaux                            | Domaines de description                                                    |                                                                                                      |                                                                |  |

|------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| d'abstraction                      | Comportement                                                               | Structure                                                                                            | Géométrie                                                      |  |

| Système/<br>Architecture           | Spécification de performances                                              | Connection<br>topologique de<br>processeurs, mémoires,<br>bus                                        | Partition en chips,<br>modules, cartes, sous-<br>systèmes      |  |

| Algorithmique                      | Description impérative                                                     | Structures de données,<br>décomposition en pro-<br>cédures                                           | ????                                                           |  |

| Transfert de<br>registres<br>(RTL) | Comportement concurrent (déclaratif), transfert de données entre registres | Connection topologique<br>de blocs<br>fonctionnels (ALU,<br>mémoires, multi-<br>plexeurs, registres) | Partition et placement<br>de blocs fonctionnels<br>(floorplan) |  |

| Logique,<br>porte                  | Equations<br>booléennes                                                    | Connection topologique de portes                                                                     | Placement et routage de cellules                               |  |

| Interrupteur                       | Equations<br>discrètes                                                     | Connection topologique de transistors                                                                | Placement et<br>routage de<br>transistors                      |  |

| Electrique                         | Equations<br>différentielles<br>non linéaires                              | Connection topo-logique d'éléments électriques (transistor, capacité, résistance, sources, etc.)     | Placement et routage d'éléments électriques de base (layout)   |  |

Table 1: Niveaux d'abstraction et domaines de description

#### 1.2. Représentation de la conception

Le processus d'abstraction consiste à ne garder que les informations nécessaires et d'ignorer *délibérément* les détails inutiles. Il permet ainsi de diminuer la quantité d'information à manipuler. On définit plusieurs *niveaux d'abstraction* (*abstraction levels*), chacun d'eux étant caractérisé par un ensemble de composants de base (primitives) et par la nature des informations qu'il considère:

- Le *niveau électrique* (*electrical level*) est le niveau le plus détaillé. Les composants de base sont les éléments électriques traditionnels (transistors, capacité, résistance, sources, etc.) dont les comportements sont représentés par des équations mathématiques impliquant des fonctions du temps ou de la fréquence.

- Le *niveau interrupteur* (*switch level*) ne considère que des transistors modélisés par des interrupteurs plus ou moins idéaux. L'information est constituée par des paires de valeurs discrètes: un niveau logique (abstraction d'une certaine tension) et une force (abstraction d'une certaine impédance). A partir de ce niveau, seule une description temporelle reste possible. Le temps peut être une valeur continue ou discrète.

- Le *niveau logique* ou *porte* (*gate level*) est basé sur l'algèbre de Boole avec quelques extensions pour introduire des aspects temporels (délais). La correspondance entre équations booléennes et portes logiques est immédiate. L'information est quantifiée sous la forme de valeurs 0 et 1, ou sous forme multi-valuée (0, 1, X, Z, ...).

- Le niveau *transfert de registres* (*register transfer level*, RTL) est une représentation synchrone du système décomposé en une partie de contrôle et une partie opérative travaillant de manière concurrente. Les composants de base sont des modules logiques complexes, tels que ALU, multiplexeur, décodeur, registre, etc. L'information est constituée par des bits et des mots et le temps est réduit à des coups d'horloge.

- Le niveau *algorithmique* (*algorithmic level*) voit le système comme un programme constitué d'une séquence d'opérations. L'information peut être de n'importe quel type et le temps peut être explicite (réduit à des coups d'horloge) ou implicite (les événements sont gérés par la causalité).

- Le niveau système (system level), ou architecture, est le niveau le moins détaillé. Le système à concevoir est vu comme un ensemble de processus communicants, mais représentant des fonctionnalités de très haut niveau comme des processeurs, des mémoires, des canaux de communication. La manière dont les processus communiquent entre eux est plus importante que le comportement des processus eux-mêmes. Le but principal est d'évaluer des réalisations de spécifications pour différentes décompositions fonctionnelles et différentes utilisations des ressources (débit de traitement, espace mémoire, etc.). Les modèles sont dits non interprétés (uninterpreted models).

A chaque niveau, il est en plus possible de représenter trois aspects, vues ou *domaines de description*, du système:

- La *vue comportementale*, représente ce que le système fait sous la forme d'un comportement entrée-sortie (boîte noire). Toute décomposition hiérarchique est purement fonctionnelle et n'implique pas forcément une structure.

- La *vue structurelle* représente comment le système est logiquement construit sous la forme d'une interconnexion de composants. Cette vue ne prend pas en compte l'aspect géométrique.

- La *vue géométrique* (*ou physique*) représente comment le système est réellement construit. Elle prend en compte les aspects de taille, de forme et de position des composants.

# Langage de description de matériel

- Description de tous les aspects d'un système matériel:

- Structure topologique, hiérarchie

- Comportement

- Assemblage, structure physique

- Description sur plusieurs niveaux d'abstraction

- Modèle logiciel d'un système matériel

- Modularité, extensibilité, typage des données

- Indépendant de:

- Technologie (MOS, bipolaire, etc.)

- Méthode de conception (top-down, bottom-up, etc.)

- Style de conception (full custom, cellules standard, FPGA, etc.)

- Outils de conception (simulateurs, synthétiseurs, etc.)

- Usage:

- Documentation

- Spécification

- Simulation

- Synthèse

#### 1.3. Langage de description de matériel

Un langage de description de matériel (*HDL – Hardware Description Language*) est un outil de description, éventuellement formel, permettant la description du comportement et de la structure d'un système matériel. Un langage de description de matériel idéal a les propriétés suivantes:

- Il supporte la description d'une large gamme de systèmes à la fois logiques (numériques) et analogiques. Pour les systèmes logiques, il supporte les systèmes combinatoires et séquentiels, synchrones et asynchrones. Pour les systèmes analogiques, il supporte non seulement des systèmes électriques, mais aussi mécaniques, thermiques, accoustiques, etc. Ce dernier aspect est très important pour la conception de systèmes car il s'agit de prendre en compte les interfaces avec l'environnement extérieur dans lequel le système conçu sera testé et dans lequel il fonctionnera.

- Il permet la description de l'état de la conception pour toutes les étapes du processus. Le fait d'utiliser un langage unique renforce la cohérence entre différentes représentations d'un même système.

- Il renforce aussi la cohérence des outils logiciels utilisés pour la simulation et la synthèse. Il peut être directement compris comme langage d'entrée pour de tels outils.

- Il est indépendant de toute méthodologie de conception, de toute technologie de fabrication et de tout outil logiciel. Il permet au concepteur d'organiser le processus de conception en fonction des besoins (conception descendante *top-down design*, conception ascendante *bottom-up design*, séparation des parties logiques et analogiques, séparation des parties de contrôle et des parties opératives, etc.).

- Il supporte plusieurs niveaux d'abstraction et autorise des descriptions hiérarchiques. Il supporte des descriptions comportementales (fonctionnelles) aussi bien que structurelles. Pour chaque niveau d'abstraction, il supporte les primitives correspondantes et leurs caractéristiques et permet d'exprimer les contraintes de conception. Un aspect important est la possibilité de spécifier des caractéristiques temporelles comme le cycle d'horloge, des délais, des temps de montée, de descente, de prépositionnement (setup time) et de maintien (hold time).

- Il est extensible: il permet au concepteur de définir de nouveaux types d'objets et les nouvelles opérations correspondantes.

- Il est plus qu'un simple format d'échange entre outils logiciels. Il renforce la communication et la cohésion à l'intérieur des équipes de conception et entre les différentes communautés de concepteurs parce qu'il est lisible (format texte) et qu'une description écrite dans un tel langage contient beaucoup d'information sur l'expertise derrière la conception. Il améliore donc grandement les phases de spécification et de documentation.

- Il est standardisé par l'intermédiaire d'organisations reconnues comme l'IEEE, l'ANSI ou l'ISO. Ceci favorise une large acceptation à la fois de la part des fournisseurs d'outils CAO et des différentes communautés de concepteurs.

# Exemple de description comportementale, structurelle et géométrique

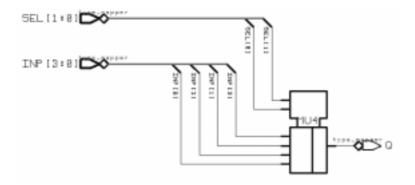

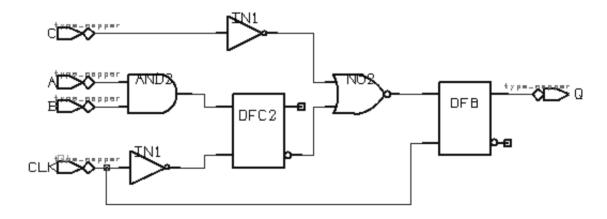

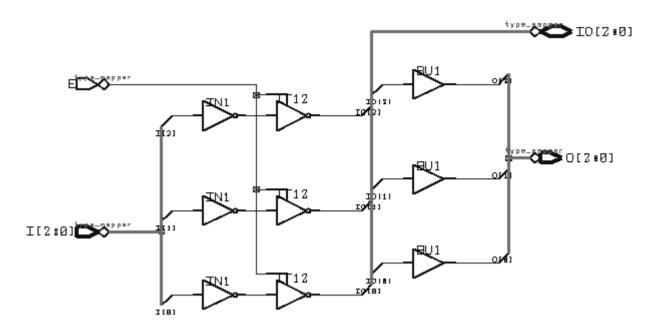

Figure 1. Description structurelle.

Figure 2. Description géométrique.

#### 1.4. Exemple de description comportementale, structurelle et géométrique

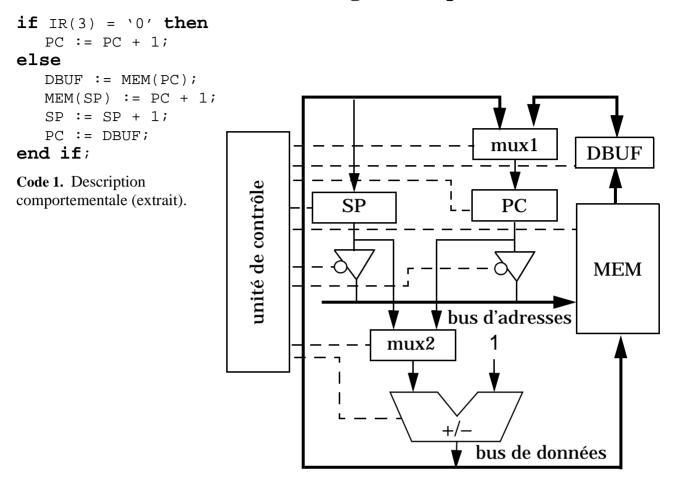

Le Code 1 donne un extrait du comportement d'une instruction d'appel conditionnel de sous-programme d'un processeur hypothétique en langage VHDL. Selon la valeur du bit 3 du registre d'instruction IR, soit le compteur de programme PC est incrémenté, soit une adresse de sous-programme est écrite dans le compteur de programme, le contexte est sauvé en mémoire en vue de l'exécution du sous-programme. Une description plus complète du comportement du processeur devrait inclure toutes les instructions et les mode d'adressages. Les opérateurs "+" et "-" sont purement abstraits à ce niveau et ne correspondent pas (encore) à des blocs fonctionnels. Il s'agira certainement d'optimiser l'usage des ressources en partageant le plus possible les blocs pour plusieurs opérations.

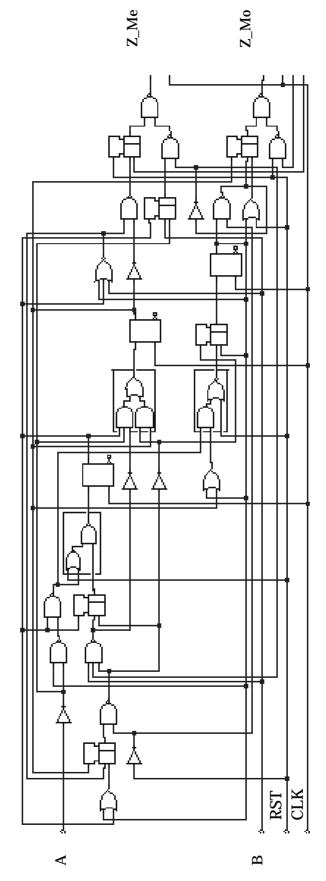

La Figure 1 illustre une description structurelle au niveau RTL correspondant au comportement du Code 1. Cette description fait apparaître des blocs fonctionnels (unité arithmétique, registres, mémoire, etc.) ainsi que les bus nécessaires aux interconnexions. La partie contrôle, responsable du séquencement des opérations, est aussi clairement identifiée. Chaque bloc fonctionnel est décrit de manière comportementale. Par exemple, la partie contrôle comme une machine à états finis, la mémoire comme un tableau à deux dimensions. Plusieurs descriptions structurelles différentes au niveau RTL sont possibles (architecture pipeline, p. ex.).

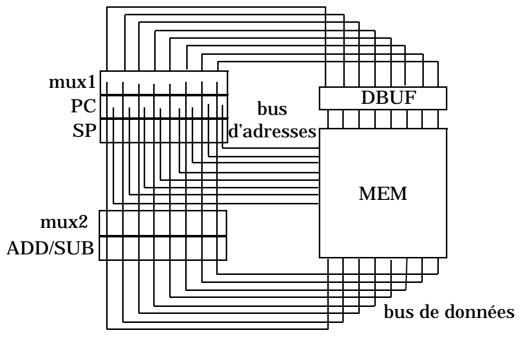

La Figure 2 illlustre une description géométrique donnant le plan d'implantation, ou *floorplan*, des blocs fonctionnels. Les dimensions et les positions relatives des blocs ont maintenant une importance. Dans cet exemple, la mémoire MEM et le registre DBUF sont placés à droite du plan, alors que les autres blocs sont groupés à gauche dans une structure dite de chemin de données (*datapath*) pour laquelle les opérateurs sont découpés en tranches de bits (*bit slices*). Les bus prennent leur forme et leur longueur finales. Il s'agit de minimiser la surface occupée et/ou les délais associés aux interconnexions.

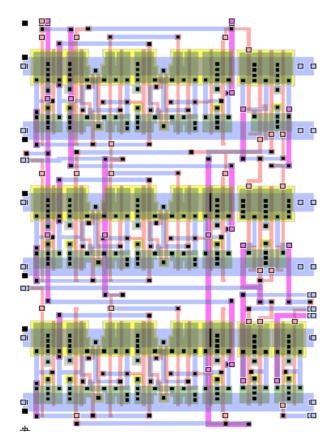

Figure 3. Exemple de layout en style cellules standard

La Figure 3 donne un autre exemple de description géométrique d'une partie de l'un des blocs de la Figure 2 (le bloc de contrôle p. ex.). Le style utilisé est celui des cellules standard. Les portes logiques sont placées et aboutées sur des rangées séparées par des canaux réservés aux interconnexions. L'implantation sur silicium de chaque transistor est décrite de manière abstraite par des polygones dont les couleurs font référence à des niveaux de fabrication (métal, polysilicium, diffusion, etc.).

# **Simulation logique**

**Figure 4.** Exemple de circuit logique réalisant la fonction A | B.

```

Tn := 0; -- temps de simulation

while Tn ð Tstop {

Tn := temps du prochain événement;

foreach entrée primaire Ek à Tn {

if Ek est active {

forall portes Gi in Fanout(Ek) { Schedule(Gi, Tn) }}

foreach porte G active à Tn {

Prendre les valeurs des entrées de G;

Calculer la nouvelle sortie de G;

if sortie de G a changé {

Calculer le délai de changement Dt;

forall portes Gi in Fanout(G) { Schedule(Gi, Tn + Dt) }}

}

}

```

Code 2. Pseudo-code simplifié de simulation logique dirigée par les événements.

#### 1.5. Simulation logique

La simulation logique a pour but la vérification de circuits intégrés de grande taille LSI et VLSI (50'000 à 1'000'000 de transistors). Il s'agit de circuits fonctionnant en mode logique qu'il n'est plus possible de vérifier au niveau électrique vu l'énorme quantité d'information qu'il faudrait stocker et gérer au niveau du transistor. Il est ainsi plus naturel et plus efficace de considérer une description du circuit à un niveau d'abstraction plus élevé, le niveau logique, pour lequel les primitives sont des portes logiques (ET, OU, NON, etc.) et les signaux représentés par des formes d'ondes logiques ne pouvant prendre qu'un nombre limité d'états. Les modèles des primitives sont simples et le circuit comporte moins d'éléments (chaque primitive regroupe en fait plusieurs transistors). De plus, l'effort nécessaire pour évaluer l'état du circuit à un moment donné est faible car l'arithmétique est basée sur des opérateurs booléens. Il est ainsi possible d'effectuer des simulations 10 à 100 fois plus rapides que les formes de simulation électrique les plus efficaces. Evidemment, la rapidité de simulation est au prix d'un appauvrissement dans le détail de l'information obtenue. Les états logiques ne représentent que partiellement les signaux électriques tension et courant et les délais doivent être modélisés séparément si l'on ne désire pas seulement effectuer une vérification fonctionnelle.

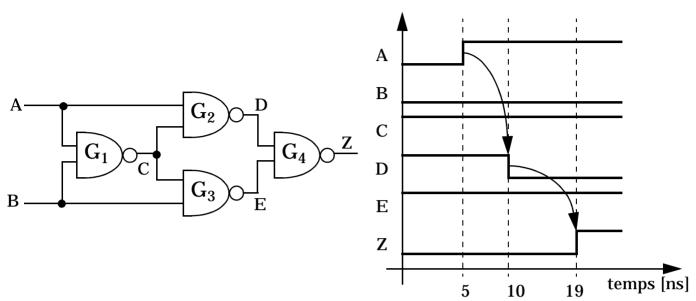

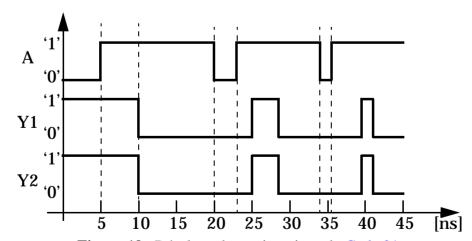

La Figure 4 illustre un circuit logique dont la sortie vaut '1' ou la valeur VRAIE si les entrées A et B sont différentes et '0' ou la valeur FAUSSE si les entrées sont les mêmes. Un chronogramme illustrant l'évolution des signaux logiques du circuit est également donné en supposant une variation de valeur sur l'entrée A.

Le Code 2 donne le pseudo-code simplifié de l'algorithme de simulation logique dirigée par les événements. Le temps est ici une variable entière multiple d'une unité de base appelée *temps de résolution minimum* (*Minimum Resolvable Time* - MRT). Toute valeur de délai non représentable entièrement dans l'échelle utilisée est tronquée (p. ex. un délai de 1,5 ns sera tronqué à 1 ns si la base de temps est la ns). L'usage d'une base de temps plus fine à par contre pour conséquence de limiter la valeur maximum du temps simulé car le codage du temps est fait avec un nombre limité de bits (32 ou 64 bits). La Table 2 donne la dynamique approximative des valeurs de temps pour différentes bases de temps.

| Base de temps | Résolution (s) | 64 bits en compl. à 2 | 32 bits en compl. à 2 |

|---------------|----------------|-----------------------|-----------------------|

| ms            | 1e-3           | 300 millions d'années | 25 jours              |

| us            | 1e-6           | 300'000 ans           | 36 minutes            |

| ns            | 1e-9           | 300 ans               | 2 secondes            |

| ps            | 1e-12          | 3 ans                 | 2 millisecondes       |

| fs            | 1e-15          | 3 heures              | 2 microsecondes       |

**Table 2:** Dynamique approximative des valeurs de temps pour différentes bases de temps.

Un événement consiste en un changement de valeur d'un signal aux entrées primaires ou aux noeuds internes du circuit. L'état du circuit n'est réévalué qu'aux instants auxquels un événement a lieu. La fonction Fanout(G) retourne l'ensemble des portes dont l'une des entrées au moins est connectée à la sortie de la porte G (p. ex.: les portes G2 et G3 font partie de l'ensemble Fanout(G1)). La procédure Schedule(G, Tn) marque la porte G comme devant être réévaluée au temps Tn.

Un aspect important de la simulation logique est le nombre d'états considérés. Le système à deux états binaires n'est pas suffisant pour modéliser et observer des états indéfinis, inconnus, ou à haute impédance. Il peut aussi être utile de modéliser des comportements résistifs au niveau logique au moyen d'états dits faibles (un '0' ou un '1' faible p. ex.).

# Synthèse logique

```

entity exsynt is

port (A, B, C, E, F, G: in bit; Z: out bit);

end;

architecture comb of exsynt is

signal X1, X2, X3: bit;

begin

Z <= (A and B) or X1;

X1 <= X3 xor G;

X2 <= E or (not F);

X3 <= C and X2;

end;</pre>

```

Code 3. Exemple de comportement combinatoire en VHDL.

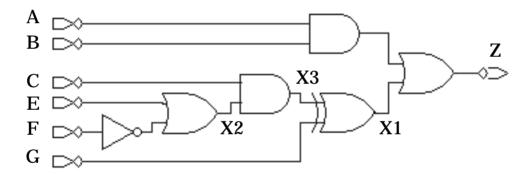

Figure 5. Circuit obtenu par traduction directe du Code 3.

Figure 6. Circuit avec chemin critique optimisé.

#### 1.6. Synthèse logique

La synthèse logique détermine une architecture au niveau logique en identifiant les portes logiques nécessaires à la réalisation des blocs définis au niveau RTL et en déterminant une interconnexion optimale de ces portes. Deux tâches principales sont effectuées:

- Une phase d'*optimisation logique* (*logic optimization* ou *logic minimization*) cherche à reformuler les équations logiques (pour un circuit combinatoire) ou à minimiser le nombre d'états (pour un circuit séquentiel) représentant la fonction d'un bloc RTL.

- Une phase d'allocation de cellules (library binding) détermine la meilleure structure à base de cellules standard dans une technologie donnée ou la meilleure programmation d'un circuit FPGA.

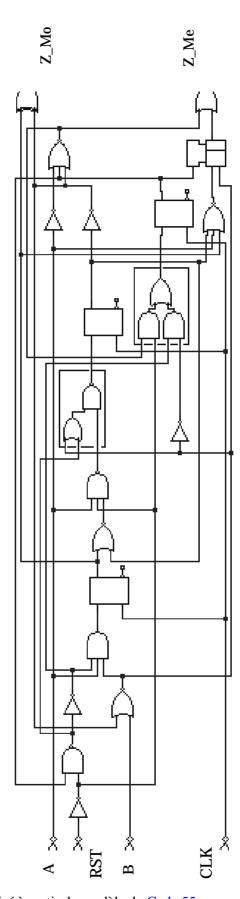

Le Code 3 donne un exemple de description VHDL d'un comportement combinatoire simple. La synthèse logique va tout d'abord compiler le modèle pour en dériver une représentation interne sous la forme d'un graphe. La Figure 5 illustre le circuit logique obtenu par traduction directe du comportement, sans optimisation. La première phase d'optimisation logique n'a pas encore eu lieu et les portes dessinées ne correspondent pas encore à des cellules d'une bibliothèque réelle, mais à des cellules génériques. La Figure 6 donne le résultat de l'optimisation logique et de l'allocation des cellules de la bibliothèque de cellules standard réelle. Dans ce cas l'optimisation a eu lieu sur le chemin critique F-X2-X3-X1-Z qui valait 1.25 ns initialement et 0.89 ns après optimisation (pour une technologie 0.6 micron CMOS). Le prix à payer est une augmentation de surface estimée de 49 microns carrés à 62 microns carrés, soit environ 27%. On parle bien d'estimation de surface ici car la place effective prise par les interconnexions n'est pas encore connue. Un modèle de calcul se basant sur le nombre de fils associés aux noeuds (équivalent à la fonction Fanout(G) discutée pour la simulation logique) a été utilisé.

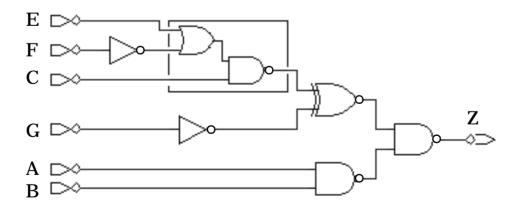

La Figure 7 donne la courbe typique surface-délai que l'on suit lorsque l'on explore l'espace des solutions avec la synthèse logique. Il n'est donc pas possible de minimiser à la fois la surface du circuit et son chemin critique. Une architecture parallèle (pipeline p. ex.) sera ainsi plus rapide qu'une architecture série, mais elle occupera plus de place à cause de la duplication nécessaire des ressources.

Figure 7. Courbe surface-délai typique pour la synthèse logique.

#### 2. VHDL

Le langage VHDL¹ permet la description de tous les aspects d'un système matériel (*hardware system*): son comportement, sa structure et ses caractéristiques temporelles. Par système matériel, on entend un système électronique arbitrairement complexe réalisé sous la forme d'un circuit intégré ou d'un ensemble de cartes. Le comportement définit la ou les fonctions que le système remplit (p. ex. le comportement d'un microprocesseur comporte, entre autres, des fonctions arithmétiques et logiques). La structure définit l'organisation du système en une hiérarchie de composants (p. ex. un microprocesseur est constitué d'une unité de contrôle et d'une unité opérative; cette dernière est elle-même, entre autres, constituée d'un composant réalisant les opérations arithmétiques entières et d'un composant réalisant les opérations arithmétiques en virgule flottante). Les caractéristiques temporelles définissent des contraintes sur le comportement du système (p. ex. les signaux d'un bus de données doivent être stables depuis un temps minimum donné par rapport à un flanc d'horloge pour qu'une opération d'écriture dans la mémoire soit valable).

La description d'un système matériel en VHDL est en plus simulable. Il est possible de lui appliquer des stimuli (également décrits en VHDL) et d'observer l'évolution des signaux du modèle dans le temps. La sémantique d'un modèle VHDL est basée sur un modèle de simulation discrète dirigée par les événements (*event-driven discrete simulation*). Le modèle VHDL ne peut prendre un nouvel état en simulation que lorsqu'un stimuli change de valeur et que ce changement est propagé dans le modèle. Le langage VHDL définit des règles précises pour l'évaluation de l'état d'un modèle en présence d'un changement de stimuli. Ces règles garantissent que l'évaluation abouti au même résultat quel que soit l'outil de simulation utilisé.

Le langage VHDL est aussi très utilisé pour la synthèse, par exemple pour dériver automatiquement un circuit à base de portes logique optimisé à partir d'une description au niveau RTL (*Register-Transfer Level*) ou algorithmique. Cette application très importante du langage sort toutefois du cadre de sa définition standard et comporte des limitations dont les plus importantes seront présentées dans ce chapitre.

Finalement, le langage VHDL est un standard IEEE<sup>2</sup> depuis 1987 sous la dénomination IEEE Std. 1076-1987 (VHDL-87). Il est sujet à une nouvelle version tous les cinq ans. La dernière version est celle de 1993 (IEEE Std. 1076-1993, VHDL-93) [LRM93][Berg93]. Elle corrige certaines incohérences de la version initiale et ajoute de nouvelles fonctionnalités.

<sup>1.</sup> VHDL est l'acronyme de VHSIC Hardware Description Language, où VHSIC signifie Very High-Speed Integrated Circuit.

<sup>2.</sup> L'IEEE (*Institute of Electrical and Electronics Engineers*) est un organisme mondial qui définit entre autres des normes pour la conception et l'usage de systèmes électriques et électroniques.

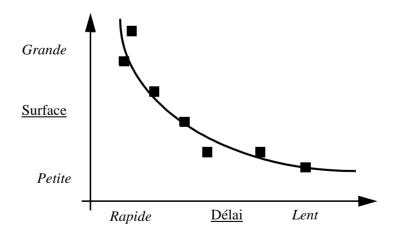

# Flot de conception basé sur VHDL

#### 2.1. Flot de conception basé sur VHDL

Le flot de conception actuel basé sur VHDL part d'une description du système à réaliser au niveau RTL. Les fonctions complexes sont décrites de manière comportementale. Par exemple, un contrôleur (ou séquenceur) est décrit comme une machine à états finis (*finite state machine*), une partie opérative comme une unité arithmétique et logique (ALU) est décrite comme un flot de données régit par des équations booléennes et contrôlé par un signal d'horloge.

Un tel modèle RTL utilise normalement un ensemble de déclarations groupées dans des paquetages (*packages*) VHDL. Ces déclarations peuvent définir les types d'information manipulés par le modèle. Par exemple, le paquetage standard IEEE STD\_LOGIC\_1164 définit un système de valeurs logiques à 9 états [STD1164].

Le modèle RTL peut être validé par simulation logique. Un environnement de test (*testbench*) peut être écrit en VHDL. Il déclare une instance du composant à tester, le modèle RTL, et un ensemble de stimulis, ou vecteurs de test. Les fonctions du système peuvent être ainsi vérifiées avant de disposer d'une réalisation détaillée de celles-ci.

Le modèle RTL peut être ensuite synthétisé. Un outil de synthèse logique (*logic synthesis*) est capable de transformer une description comportementale en un circuit optimisé à base de portes logiques (*gate-level netlist*). L'optimisation est gouvernée par un ensemble de contraintes fournies par l'utilisateur sur la surface et/ou les délais que doit satisfaire le circuit. La définition de ces contraintes est faite dans un langage propre à l'outil de synthèse. La synthèse se base aussi sur une bibliothèque de synthèse contenant les descriptions de toutes les cellules (portes) disponibles dans la technologie utilisée (p. ex. 0.6 micron CMOS). Les informations essentielles sont, pour chaque cellule: sa fonction (p. ex. NAND, flip-flop), sa surface et les délais associés à ses chemins d'entrées-sorties. Là aussi le format de la bibliothèque dépend de l'outil de synthèse.

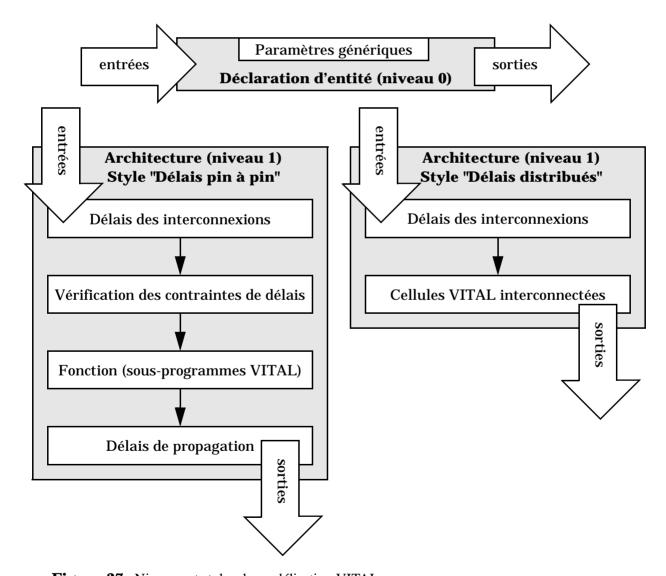

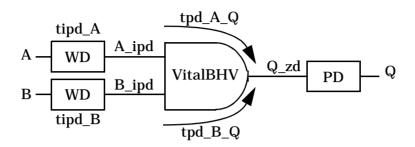

Le résultat de la synthèse logique est un circuit de portes logiques dont on peut en tirer une nouvelle description VHDL. Les modèles VHDL des portes logiques sont stockés dans une bibliothèque mise à disposition par le fournisseur technologique (fondeur ou fabricant FPGA). Ces modèles de portes sont usuellement définis selon la norme VITAL (VHDL Initiative Towards VHDL Libraries) [STD1076.4] pour permettre la rétroannotation des délais dûs aux interconnexions. La simulation après synthèse logique ne prend cependant en compte que les délais des portes.

La réalisation du circuit sous forme de layout est faite par un outil de placement et de routage qui nécessite une description d'entrée dans un format différent de VHDL. Les formats EDIF (pour les cellules standard) ou XNF (pour les FPGA de type Xilinx) sont alors utilisés. Une fois le layout obtenu il est possible d'en extraire les valeurs des éléments parasites (résistances, capacités) associés aux interconnexions et de calculer les délais correspondants. Ces délais sont stockés dans un fichier au format SDF (*Standard Delay Format*) [SDF], puis réinjectés dans la description VHDL obtenue après synthèse logique (rétroannotation, *backannotation*). Cette foisci la simulation prend en compte les délais des portes logiques et des interconnexions. Les résultats sont suffisamment précis pour que les fondeurs les acceptent comme référence (*sign-off simulation*) sans qu'il soit nécessaire de recourir à des simulations au niveau électrique (de type SPICE) coûteuses.

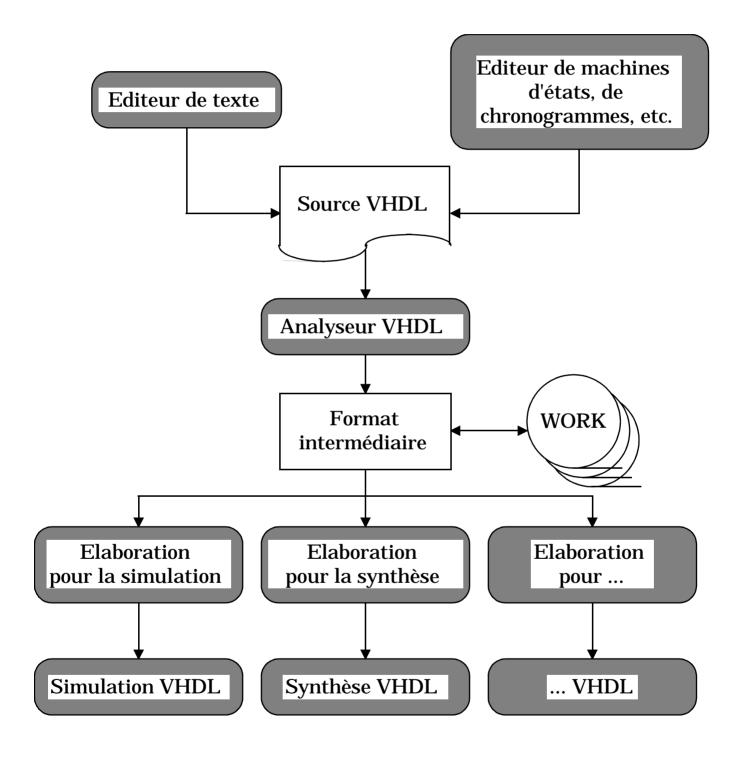

### **Environnement de travail VHDL**

#### 2.2. Environnement de travail VHDL

L'interface graphique peut se réduire à un simple éditeur de texte. Les outils CAO du marché utilisent en plus leur éditeur de schémas pour générer automatiquement le squelette d'un modèle VHDL, c'est-à-dire au moins la déclaration d'entité avec ses ports et un corps d'architecture minimum. Des outils plus avancés permettent de décrire le comportement du système à modéliser sous la forme de machines d'états, de chronogrammes ou de tables de vérité.

L'analyseur (ou compilateur) vérifie la syntaxe d'une description VHDL. Il permet la détection d'erreurs locales, qui ne concernent que de l'unité compilée. Plusieurs techniques d'analyse sont actuellement utilisées par les outils du marché. L'approche compilée produit directement du code machine, ou, dans certains cas, du code C qui sera lui-même compilé. L'objet binaire est alors lié au code objet du simulateur. Cette approche réduit le temps de simulation au détriment du temps d'analyse. L'approche interprétée transforme le code source en un pseudo-code qui est interprété par le simulateur. Cette approche réduit le temps d'analyse au détriment du temps de simulation.

Chaque concepteur possède une *bibliothèque de travail* (*working library*) de nom logique WORK (le nom est standard) dans laquelle sont placés tous les modèles compilés. Le lien du nom logique avec l'emplacement physique de la bibliothèque dépend de l'outil de simulation ou de synthèse utilisé.

Il est aussi possible de faire référence, en mode de lecture seule, à d'autres bibliothèques, des *bibliothèques de ressources*, contenant d'autres modèles ou des utilitaires. Plusieurs bibliothèques peuvent être actives simultanément. Chaque bibliothèque contient une collection de modèles mémorisés dans un format intermédiaire. Elle contient également un certain nombre de relations et d'attributs liant, si nécessaire, les différents modèles entre eux.

Le *simulateur* calcule comment le système modélisé se comporte lorsqu'on lui applique un ensemble de stimuli. L'environnement de test peut également être écrit en VHDL: il peut être lui-même vu comme un système définissant les stimuli et les opérations à appliquer aux signaux de sortie pour les visualiser (sous forme texte ou graphique). Le simulateur permet aussi le déverminage (*debugging*) d'un modèle au moyen de techniques analogues à celles proposées pour les programmes écrits en Pascal, C ou Ada: simulation pas à pas, visualisation de variables, de signaux, modification interactive de valeurs, etc.

Un *outil de synthèse* est capable de générer une netlist de portes logiques (synthèse logique), et même maintenant une architecture RTL (synthèse de haut niveau), à partir d'une description VHDL comportementale. Le résultat de la synthèse peut lui aussi être décrit en VHDL pour simulation. Un tel outil n'accepte en général qu'un sous-ensemble du langage [Airi94] [Ott94] [Bhas96] [STD1076.3].

La phase d'élaboration est propre à chaque application (simulation, synthèse, etc.). Elle consiste en une construction des structures de données et permet la détection d'erreurs globales, qui concernent l'ensemble des unités de la description. Cette phase est normalement cachée pour la simulation, alors qu'elle est explicite pour la synthèse. En effet, dans ce dernier cas elle permet de dériver une structure générique, indépendante de la technologie cible, sur laquelle il est possible de définir des contraintes qui gouverneront la phase d'optimisation.

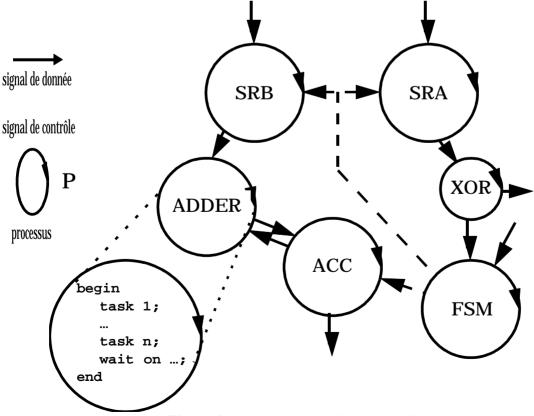

# Modèle sémantique de VHDL

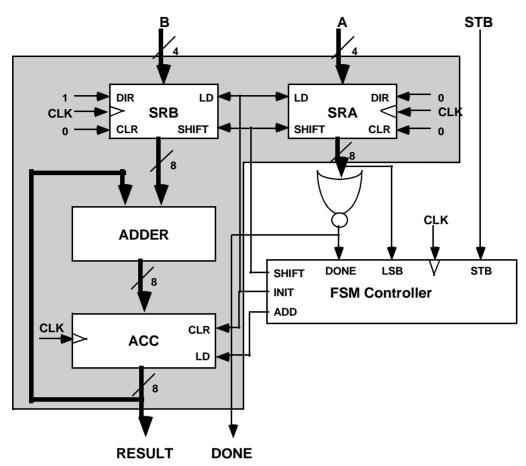

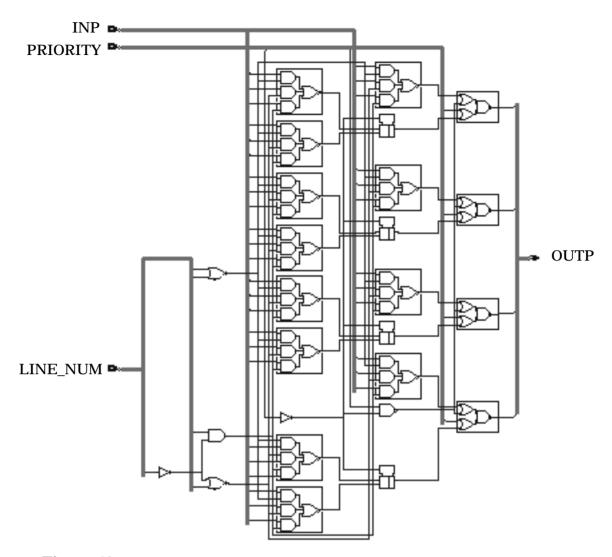

Figure 8. Vue RTL d'un multiplieur à additions et décalages.

Figure 9. Vue "processus" du multiplieur.

#### 2.3. Modèle sémantique de VHDL

Tout modèle VHDL peut se ramener à un ensemble de *processus concurrents* dont l'exécution peut être activée de manière individuelle (asynchrone) en fonction de l'activité de *signaux*. Chaque processus est sensible sur un certain nombre de signaux dont les événements (les changements de valeurs) activent l'exécution des instructions du processus. Ces instructions sont exécutées de manière séquentielle dans l'ordre de leur apparition. Les signaux représentent ainsi le moyen de communiquer des informations de manière globale dans le modèle VHDL<sup>1</sup>.

Un *cycle de simulation canonique* fait partie de la définition du langage VHDL. Il définit la manière de mettre à jour les signaux et à quel moment les processus doivent être activés. Il faut noter que l'ordre d'exécution des processus activés peut être quelconque et dépend de l'outil de simulation. Il est toutefois garanti que les signaux possèdent les mêmes valeurs à la fin d'un cycle de simulation quelque soit l'ordre d'exécution des processus.

Le modèle VHDL d'un système complexe est normalement décrit de manière hiérarchique comme une structure de composants. Chaque composant peut encapsuler du comportement sous forme de processus concurrents.

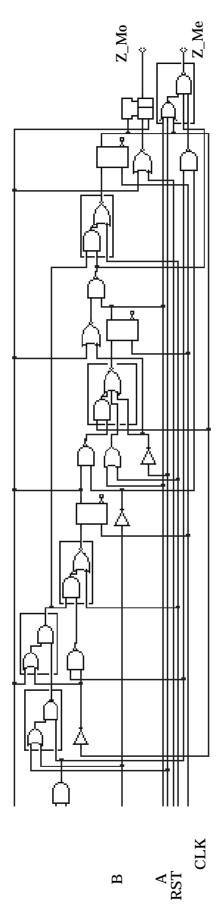

A titre d'exemple, considérons le modèle au niveau RTL d'un multiplieur de deux mots de 4 bits A et B réalisant l'algorithme classique basé sur des additions et des décalages successifs (Figure 8). La description est structurelle et définit les composants de la partie contrôle (le contrôleur FSM) et de la partie opérative (les registres SRA et SRB, l'additionneur ADDER et l'accumulateur ACC). On suppose que le comportement de chaque composant est décrit séparément comme une série d'instructions à exécuter en séquence.

Le modèle VHDL du multiplieur peut être vu comme un ensemble de processus concurrents, chaque processus correspondant à un composant (Figure 9). Les processus sont liés entre eux par un réseau de signaux qui représentent les données et les signaux de contrôle. L'activité de ces signaux conditionne l'exécution des processus. Dès qu'un processus est activé il exécute ses instructions jusqu'à un point d'arrêt. Le point d'arrêt est une instruction VHDL particulière qui dit essentiellement d'attendre jusqu'à ce qu'il y ait un nouvel événement sur les signaux sensibles du processus. L'exécution d'un processus est *cyclique*: la séquence d'instructions recommence au début une fois la dernière instruction exécutée.

Par exemple, un flanc montant du signal d'horloge CLK et un signal SHIFT actif - égal à '1' - va simultanément<sup>2</sup> effectuer un décalage à gauche du registre SRB et à droite du registre SRA. Une fois les opérations effectuées chaque processus se met en état de veille jusqu'à ce qu'un nouvel événement significatif le réactive à nouveau.

Toutes les données nécessaires à l'exécution d'un processus (p. ex. des variables locales) sont ainsi créées avant de démarrer la simulation proprement dite et ne sont détruites qu'à la fin de la simulation.

<sup>1.</sup> VHDL-93 supporte aussi le concept de variables globales (*shared variables*), mais leur usage est plus délicat. L'accès simultané à la même variable globale à partir de plusieurs processus n'est pas déterministe.

<sup>2.</sup> L'effet sera effectivement simultané pour l'utilisateur, même si les deux processus SRA et SRB sont activés l'un après l'autre dans un ordre quelconque.

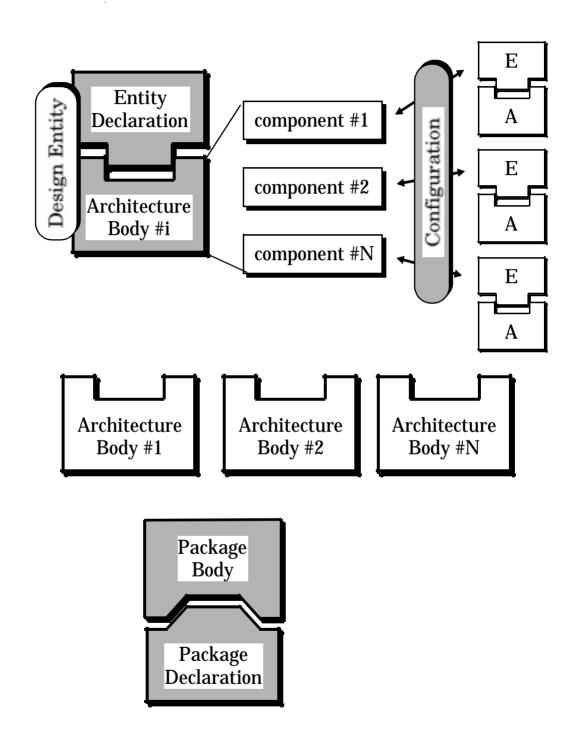

# Organisation d'un modèle VHDL

Figure 10. Unités de conception VHDL (en gris).

#### 2.4. Organisation d'un modèle VHDL

#### Unités de conception

L'unité de conception (design unit) est le plus petit module compilable séparément. VHDL offre cinq types d'unités de conception (Figure 10):

- la déclaration d'entité (*entity declaration*);

- le corps d'architecture (architecture body), ou plus simplement architecture;

- la déclaration de configuration (configuration declaration);

- la déclaration de paquetage (package declaration);

- le corps de paquetage (package body).

Les trois premières unités de conception (déclaration d'entité, architecture et déclaration de configuration) permettent la description de l'aspect matériel d'un système, alors que les deux dernières (déclaration et corps de paquetage) permettent de grouper des informations pouvant être réutilisées pour la description de plusieurs systèmes différents.

Les trois unités de conception: déclaration d'entité, déclaration de configuration et déclaration de paquetage, sont qualifiées de *primaires* (*primary unit*), car elles décrivent une vue externe (le "quoi" de la boîte noire). Les unités primaires déclarent ce qui est accessible aux autres parties du modèle. Elles permettent le partage et la réutilisation de ressources (modèles et algorithmes). Elles ne contiennent que le minimum d'information nécessaire pour l'utilisation de ces ressources.

Les deux autres unités de conception: architecture et corps de paquetage, sont qualifiées de *secondaires* (*secondary units*), car elles décrivent une vue interne particulière (une réalisation ou le "comment" de la boîte noire). Les unités secondaires regroupent des ressources seulement visibles par leur unité primaire correspondante (déclaration d'entité pour l'architecture et déclaration de paquetage pour le corps de paquetage). Elles contiennent des détails d'implémentation que l'on masque pour a) éviter de surcharger l'utilisateur avec des détails inutiles et/ou b) éviter des modifications malencontreuses de modèles et d'algorithmes de base. Plusieurs unités secondaires peuvent être définies pour une même unité primaire.

#### Entité de conception

L'entité de conception (design entity) est l'abstraction de base en VHDL. Elle représente une portion d'un système matériel possédant une interface entrée-sortie et une fonction bien définies. Une entité de conception est constituée d'une déclaration d'entité et d'un corps d'architecture correspondant.

Une entité de conception peut représenter un système matériel à plusieurs niveaux de complexité: un système entier, un sous-système, une carte, un circuit intégré, une cellule complexe (p.ex. ALU, mémoire, etc.), une porte logique.

Une *configuration* (*configuration*) permet de définir comment plusieurs entités de conception sont assemblées pour constituer le système complet. Une entité de conception peut être décrite comme une hiérarchie de *composants* (*component*) interconnectés. Chaque composant peut être lié à une entité de conception de plus bas niveau qui définit la structure ou le comportement de ce composant. Une telle décomposition d'une entité de conception et les liens de ses composants éventuels à d'autres unités de conception forment une hiérarchie représentant le système complet.

# Modèle comportemental d'un registre 4 bits

**Code 5.** Modèle comportemental du registre 4 bits. Fichier: reg4\_bhv.vhd.

end process;

end architecture bhv;

#### 2.5. Modèles VHDL d'un registre 4 bits

On donne ici plusieurs versions possibles d'un modèle de registre 4 bits en VHDL pour illustrer l'usage des différentes unités de conception et des styles de description disponibles en VHDL. Se référer à l'Annexe A pour plus de détails sur la syntaxe du langage. Les mots-clés réservés du langage sont indiqués en caractères gras.

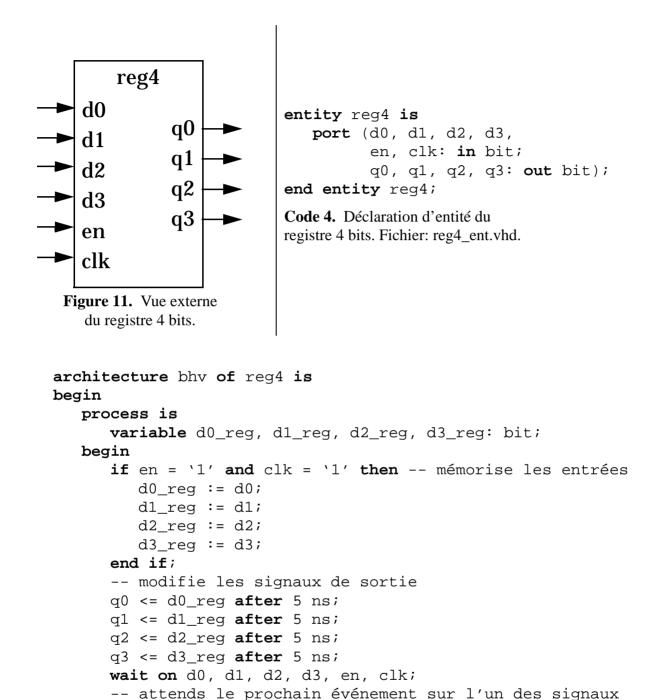

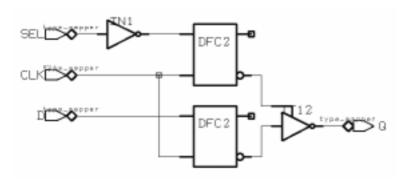

#### Déclaration d'entité

La Figure 11 illustre la vue externe du registre 4 bits. Le registre a pour nom REG4 et possède 6 entrées (les données D0, D1, D2, D3 et le signal de contrôle EN et l'horloge CLK) et 4 sorties (les données Q0, Q1, Q2, et Q3). Le Code 4 définit la déclaration d'entité VHDL du registre. On peut distinguer les aspects principaux suivants:

- Les *ports* (*ports*) définissent les canaux de communication entre le modèle et le monde extérieur. Plus précisément ils définissent les types de signaux transitant par ces canaux ainsi que les directions de transition. Dans l'exemple, tous les signaux sont du type prédéfini bit, c'est-à-dire pouvant prendre la valeur '0' ou '1', et les signaux d'entrées (resp. de sortie) sont définis par le *mode* in (resp. par le mode out).

- La déclaration d'entité peut être stockée dans un fichier dont le nom suggéré est reg4\_ent.vhd. Elle peut être compilée et le résultat de la compilation sera placé dans la bibliothèque de travail WORK.

#### **Architecture comportementale**

Le Code 5 donne le corps d'architecture définissant un modèle comportemental du registre. On peut distinguer les aspects principaux suivants:

- L'architecture a pour nom BHV et fait référence à la déclaration d'entité de nom REG4. Tous les objets déclarés dans l'entité (ici les signaux d'interface) sont visibles dans l'architecture sans déclaration supplémentaire.

- Le comportement du registre est défini à l'aide d'un processus unique délimité par les mots-clés **process** et **end process**. Le processus définit une séquence d'instructions qui:

- 1) mémorisent conditionnellement l'état des entrées du registre lorsque le signal EN et l'horloge CLK sont actifs (ici égaux à la valeur '1'),

- 2) modifient les valeurs des signaux de sortie du registre avec un délai de 5 ns (ce délai modélise le fait que le registre réel ne réagira pas de manière instantanée),

- 3) mettent le processus en état de veille jusqu'à un prochain événement *sur l'un quelconque* des signaux d'entrée (instruction wait).

- Un événement sur l'un des signaux d'entrée du registre réactivera le processus qui exécutera ses instructions en repartant de la première instruction après le mot-clé **begin**.

- Le processus déclare quatre variables locales de type bit qui servent à mémoriser l'état interne du registre. Ces variables sont initialisées à la valeur '0' au début de la simulation et conservent leurs valeurs d'une activation du processus à l'autre.

- Le corps d'architecture peut être stocké dans un fichier propre dont le nom suggéré est reg4\_bhv.vhd. Il peut être compilé et le résultat de la compilation sera placé dans la bibliothèque de travail WORK.

<sup>1.</sup> Un certain nombre de déclarations sont prédéfinies en VHDL et stockées dans le paquetage nommé STAND-ARD de la bibliothèque nommée STD.

# Modèle structurel d'un registre 4 bits

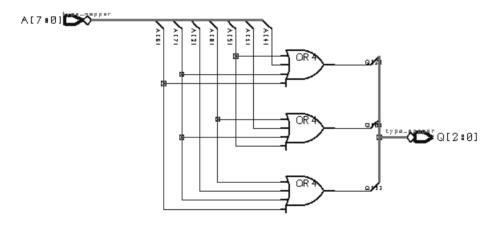

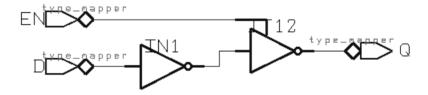

**Figure 12.** Vue structurelle du registre 4 bits.

```

architecture str of reg4 is

```

```

-- déclaration des composants utilisés

component and2 is

port (i1, i2: in bit; z: out bit);

end component and2;

component dlatch is

port (d, clk: in bit; q: out bit);

end component dlatch;

signal int_clk: bit; -- signal interne

begin

-- instances de latches

bit0: dlatch port map (d => d0, clk => int_clk, q => q0);

bit1: dlatch port map (d => d1, clk => int_clk, q => q1);

bit2: dlatch port map (d => d2, clk => int_clk, q => q2);

bit3: dlatch port map (d => d3, clk => int_clk, q => q3);

-- génération de l'horloge interne

gate: and2 port map (en, clk, int_clk);

end architecture str;

```

Code 6. Modèle structurel du registre 4 bits. Fichier: reg4\_str.vhd.

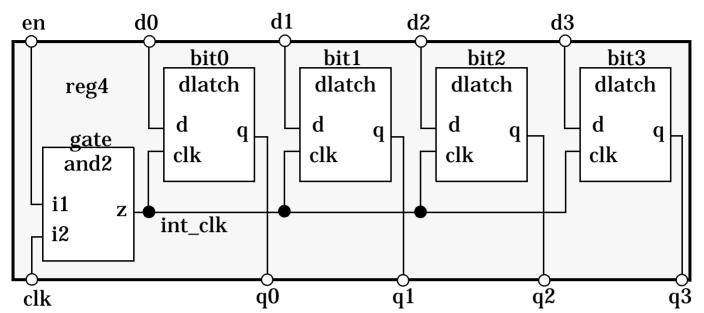

#### **Architecture structurelle**

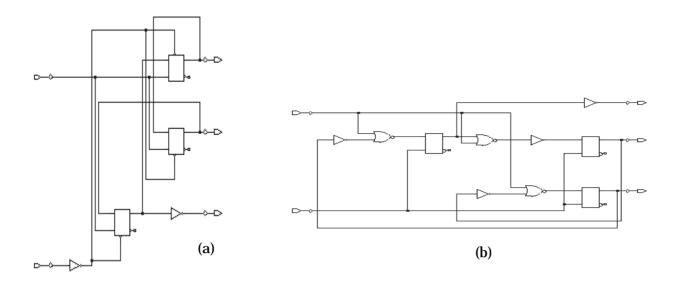

La Figure 12 représente une vue structurelle du registre 4 bits composée de composants de types latch et porte AND interconnectés. Le Code 6 donne l'architecture VHDL correspondante. On peut distinguer les aspects principaux suivants:

- L'architecture nommée STR fait référence à la même déclaration d'entité que le modèle comportemental précédant, ce qui est normal vu que la vue externe du modèle reste la même.

- L'architecture reflète fidèlement la structure de la Figure 12. Elle déclare dans un premier temps les composants nécessaires LATCH et AND2 dont un certain nombre d'instances seront "placées" dans le modèle.

- Chaque instance de composant définit les associations entre ses *ports formels* (*formal ports*), c'est-à-dire les ports définis dans sa déclaration, et ses *ports effectifs* (*actual ports*), c'est-à-dire les signaux d'interface ou le signal local du registre. Dans l'exemple, les instances de latches utilisent une *association par nom* (*named association*), alors que l'instance de la porte AND2 utilise une *association par position* (*positional association*).

- L'étiquette (label), telle que BITO, est obligatoire pour nommer chaque instance de manière unique.

- L'ordre de déclaration des instances de composants peut être quelconque. Chaque instance peut être vue comme un processus activable par un événement sur l'un des signaux effectifs associé à un port formel de mode in.

- Les modèles des composants utilisés ne sont pas définis à ce niveau et qu'une étape de *configuration* sera encore nécessaire pour rendre le modèle structurel du registre simulable. Le rôle de la configuration est d'associer une entité de conception (paire entité/architecture) à chaque instance de composant. C'est pourquoi les noms des composants déclarés et de leurs ports formels peuvent être quelconques.

- Le corps d'architecture peut être stocké dans un fichier propre dont le nom suggéré est reg4\_str.vhd. Il peut être compilé et le résultat de la compilation sera placé dans la bibliothèque de travail WORK.

#### Environnement de test

```

entity reg4_tb is

end entity reg4_tb;

architecture test of reg4_tb is

component c_reg4 is

port (p_d0, p_d1, p_d2, p_d3, p_en, p_clk: in bit;

p_q0, p_q1, p_q2, p_q3: out bit);

end component c_reg4;

signal s_d0, s_d1, s_d2, s_d3, s_en, s_clk,

s_q0, s_q1, s_q2, s_q3: bit;

begin

-- composant à tester

UUT: c_reg4 port map (s_d0, s_d1, s_d2, s_d3, s_en, s_clk,

s_q0, s_q1, s_q2, s_q3);

-- stimulis

s_clk <= not s_clk after 20 ns; -- période de 40 ns

process

begin

s_d0 <= '1'; s_d1 <= '1'; s_d2 <= '1'; s_d3 <= '1';

s_en <= '0';

wait for 40 ns;

s_en <= `1';

wait for 40 ns;

s_d0 <= '0'; s_d1 <= '0'; s_d2 <= '0'; s_d3 <= '0';

wait for 40 ns;

s_en <= '1';

wait for 40 ns;

. . .

wait;

end process;

end architecture test;

```

**Code 7.** Modèle VHDL de l'environnement de test. Fichier: reg4\_tb.vhd.

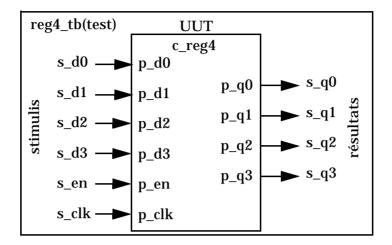

#### Environnement de test

L'environnement de test (*testbench*) d'un modèle VHDL peut être lui-même décrit comme un modèle VHDL. La Figure 13 illustre la structure d'un tel environnement.

Figure 13. Environnement de test du registre 4 bits.

Le modèle à tester est instancié comme un composant d'un modèle qui ne possède pas d'interactions avec le monde extérieur. Le reste du modèle définit les stimulis à appliquer au composant testé et un traitement éventuel des résultats obtenus aux sorties du composant. Un environnement de test VHDL est usuellement un mélange de structure et de comportement.

Le Code 7 donne le modèle VHDL de l'environnement de test du modèle du registre 4 bits. Les points suivants sont à considérer:

- La déclaration d'entité se limite à sa plus simple expression.

- Le composant à tester est déclaré puis instancié. Pour l'instant rien ne lie l'instance de composant avec une entité de conception particulière. Il s'agit encore de définir une *configuration* pour rendre l'environnement de test simulable.

- Le comportement du signal d'horloge CLK est défini au moyen d'une assignation concurrente de signal. Le signal CLK a une valeur initiale par défaut égale à '0', qui est la première valeur du type énuméré prédéfini bit. Le signal aura une période de 40 ns.

- Les autres stimulis sont définis dans un processus. Plusieurs séquences de stimulis délimitées par des instructions wait sont définies. Losrque tous les stimulis ont été appliqués, la dernière instruction wait sans paramètre stoppe le processus indéfiniment.

- Le modèle ne contient pas d'instructions particulières pour le traitement des résultats, c'est-à-dire des signaux Q0, Q1, Q2 et Q3. On se contente dans ce cas de visualiser les formes d'ondes dans l'environnement de simulation.

- Un environnement de test plus élaboré pourrait contenir des composants supplémentaires pour la génération des stimulis et le traitement des signaux de sortie.

- Comme la déclaration d'entité est très simple, il est recommandé de maintenir la déclaration d'entité et le corps d'architecture dans le même fichier dont le nom suggéré est reg4\_tb.vhd. La compilation de ce fichier va créer *deux* unités de conception dans la bibliothèque de travail WORK.

# Déclaration de configuration

```

architecture test of reg4_tb is

component c req4 is

port (p_d0, p_d1, p_d2, p_d3, p_en, p_clk: in bit;

p_q0, p_q1, p_q2, p_q3: out bit);

end component c req4;

begin

end architecture test;

configuration reg4_cfg_tb_bhv of reg4_tb is

for test

for UUT: c_reg4 use entity WORK.reg4(bhv)

port map (d0 => p_d0, d1 => p_d1, d2 => p_d2, d3 => p_d3,

en => p_en, clk => p_clk,

q0 \Rightarrow p_q0, q1 \Rightarrow p_q1, q2 \Rightarrow p_q2, q3 \Rightarrow p_q3);

end for; -- UUT

end for; -- test

end configuration reg4_cfg_tb_bhv;

```

**Code 8.** Déclaration de configuration pour le test du modèle comportemental du registre 4 bits. Fichier: reg4\_cfg\_tb\_bhv.vhd.

**Code 9.** Déclaration de configuration pour le test du modèle structurel du registre 4 bits. Fichier: reg4\_cfg\_tb\_str.vhd.

### Déclaration de configuration

La déclaration de configuration définit la vue de plus haut niveau d'un modèle. Elle définit les associations globales entre les instances de composants d'une architecture et les entités de conception disponibles dans une biblothèque (WORK ou autre).

Le Code 8 donne la déclaration de configuration de l'environnement de test du registre 4 bits utilisant le modèle comportemental du registre (Code 5).

- On suppose que l'entité de conception reg4 (bhv) a déjà été compilée sans erreur dans la bibliothèque WORK.

- L'association **port map** est nécessaire parce que les noms donnés aux ports de la déclaration de composant dans l'environnement de test ne sont pas identiques à ceux de la déclaration d'entité du registre. Cette association pourrait être omise si les noms étaient identiques.

- La déclaration de configuration est stockée dans un fichier dont le nom suggéré est reg4\_cfg\_tb\_bhv.vhd.

Le test de l'architecture structurelle du registre requiert la définition d'une autre configuration sans qu'il soit nécessaire de modifier le modèle de l'environnement de test. Le Code 9 donne la nouvelle déclaration de configuration.

- On suppose que les entités de conception des portes DLATCH (Code 10) et AND2 (Code 11) ont été préalablement compilées sans erreur dans la bibliothèque GATES.

- La déclaration de configuration comporte dans ce cas un niveau hiérarchique supplémentaire pour associer les instances de portes logiques.

- Comme les noms des ports de la déclaration d'entité DLATCH sont identiques à ceux de la déclaration du composant du même nom dans l'architecture STR, la partie port map n'est pas nécessaire.

- La déclaration de configuration est stockée dans un fichier dont le nom suggéré est reg4\_cfg\_tb\_str.vhd.

Les déclarations de configurations dans cet exemple représentent les descriptions de plus haut niveau du modèle. Ce sont les unités de conception à charger dans un simulateur. Toutes les autres unités de conception qui en dépendent seront chargées dynamiquement avant la phase d'élaboration.

### Déclaration de configuration (suite)

```

entity dlatch is

entity and2 is

port (d, clk: in bit;

port (a, b: in bit;

: out bit);

: out bit);

Z

end entity dlatch;

end entity and2;

architecture bhy of dlatch is

architecture bhy of and2 is

begin

begin

process is

process is

begin

begin

if clk = '1' then

z <= a and b after 2 ns;

q <= d after 2 ns;

wait on a, b;

end if;

end process;

end architecture bhv;

wait on clk, d;

end process;

end architecture bhv;

```

Code 10. Modèle comportemental d'un composant latch. Fichier: dlatch\_bhv.vhd.

**Code 11.** Modèle comportemental d'un composant and 2. Fichier: and 2\_bhv.vhd.

```

library GATES;

architecture str2 of reg4 is

signal int_clk: bit; -- signal interne

begin

-- instanciations directes des latches

bit0: entity GATES.dlatch(bhv)

port map (d => d0, clk => int_clk, q => q0);

bit1: entity GATES.dlatch(bhv)

port map (d => d1, clk => int_clk, q => q1);

bit2: entity GATES.dlatch(bhv)

port map (d => d2, clk => int_clk, q => q2);

bit3: entity GATES.dlatch(bhv)

port map (d => d3, clk => int_clk, q => q3);

-- instanciation directe de la porte and2

gate: entity GATES.and2(bhv)

port map (en, clk, int_clk);

end architecture str2;

```

Code 12. Instanciation directe.

#### **Instanciation directe**

L'instanciation directe (direct instantiation) a été introduite en VHDL-93 pour offrir une version simplifiée du mécanisme de configuration. Il n'est plus nécessaire de déclarer de composants et de configuration. Chaque instance est directement associée à une entité de conception.

Le Code 12 donne une nouvelle version de l'architecture structurelle du registre 4 bits utilisant l'instanciation directe. Chaque instance doit être associée indépendemment à une entité de conception. Il n'est pas possible d'utiliser de spécification **for all** dans ce cas.

### Spécification de configuration

La *spécification de configuration* (*configuration specification*) est une autre forme de configuration qui ne définit pas une nouvelle unité de conception. Elle revient à définir l'association d'une instance de composant avec son entité de conception correspondante directement dans le corps d'architecture, en nécessitant toutefois toujours une déclaration de composant préalable. Le Code 13 donne des exemples de spécifications de configurations pour l'architecture structurelle du registre 4 bits. Dans ce cas, la déclaration de configuration de l'environnement de test du Code 9 s'en trouve simplifiée.

```

library GATES;

architecture str2 of reg4 is

component and2 is

port (i1, i2: in bit; z: out bit);

end component and2;

for all: and2 use entity GATES.and2(bhv) port map (i1, i2, z);

component dlatch is

port (d, clk: in bit; q: out bit);

end component dlatch;

for all: dlatch use entity GATES.dlatch(bhv);

...

begin

...

end architecture str2;

```

**Code 13.** Utilisation de spécifications de configurations pour l'architecture structurelle du registre 4 bits; le reste du modèle est identique à celui du Code 6.

#### Remarque

Il existe une forte ressemblance entre une déclaration de composant et une déclaration d'entité. Une différence essentielle est que la déclaration d'entité définit ce que le modèle d'un composant offre au monde extérieur, alors que la déclaration de composant définit ce dont le modèle qui utilise des instances de ce composant a besoin. D'une manière imagée on peut dire que la déclaration de configuration permet de relier l'offre à la demande lorsque ces dernières n'utilisent pas les mêmes conventions de nommage des paramètres ou des ports.

## Modèles génériques

- Paramètres (constantes) génériques

- Objets d'interface non contraints

- Instruction concurrente generate

```

entity dff is

generic (Tpd_clk_q, -- temps de propagation

Tsu_d_clk, -- temps de prépositionnement

Th_d_clk: delay_length); -- temps de maintien

port (clk, d: in: bit; q: out bit);

end entity dff;

architecture bhy of dff is

begin

behavior: q <= d after Tpd_clk_q when clk = '1' and clk'event;

check_setup: process is

begin

wait until clk = '1';

assert d'last_event >= Tsu_d_clk report "Setup violation";

end process check_setup;

check_hold: process is

begin

wait until clk'delayed(Th_d_clk) = `1';

assert d'delayed'last_event >= Th_d_clk

report "Hold violation";

end process check hold;

end architecture bhy;

FF1: entity WORK.dff(bhv)

generic map (Tpd_clk_q => 4 ns,

Tsu_d_clk \Rightarrow 3 ns, Th_d_clk \Rightarrow 1 ns

port map (clk => master_clk, d => data, q => data_reg);

```

**Code 14.** Exemple d'utilisation de paramètres génériques spécifiant les caractéristiques temporelles d'un modèle de flip-flop D et exemple d'instance de composant avec spécification des valeurs effectives pour les paramètres.

### 2.6. Modèles génériques

VHDL permet le développement de modèles dont le comportement ou la structure peuvent être paramétrés au moyen de trois mécanismes complémentaires:

- Les paramètres génériques.

- Les objets d'interface non contraints.

- L'instruction concurrente generate.

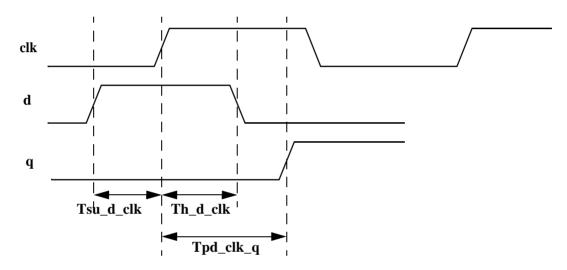

#### Paramètres génériques

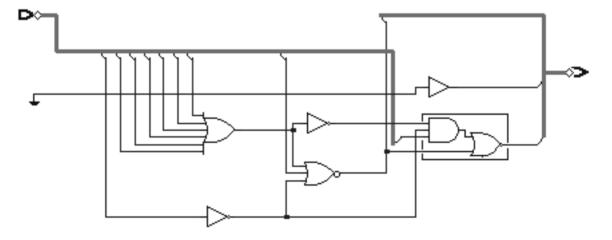

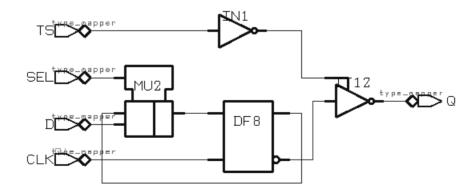

Le Code 14 donne l'exemple d'un modèle de flip-flop D pour lequel les caractéristiques temporelles (temps de propagation TPD\_CLK\_Q, temps de prépositionnement (*setup time*) TSU\_D\_CLK et temps de maintien (*hold time*) TH\_D\_CLK) sont définis comme des paramètres génériques.

Figure 14. Paramètres temporels du flip-flop D.

Le corps d'architecture est composé de trois processus concurrents. Le premier, nommé behavior, définit le comportement du composant en tenant compte du temps de propagation. Le deuxième, nommé check\_setup, vérifie le temps de prépositionnement. Le troisième, nommé check\_hold, vérifie le temps de maintien. Noter l'usage des attributs prédéfinis sur les signaux 'last\_event et 'delayed.

Les valeurs effectives des paramètres seront spécifiées pour chaque instance du composant au moyen d'une spécification generic map.

## Modèles génériques (suite)

```

entity reg is

port (clk, rst: in bit; d: in bit_vector; q: out bit_vector);

begin

assert d'length = q'length;

end entity reg;

architecture bhv of reg is

begin

process (clk, rst) is

constant zero: bit_vector(q'length) := (others => '0');

begin

if rst = '1' then

q <= zero;

elsif clk'event and clk = '1' then

q <= d; -- erreur si d'length /= q'length!

end if;

end process;

end architecture bhv;

signal data, data_reg: bit_vector(15 downto 0);

regA: entity WORK.reg(bhv) port map (data, data_reg);

Code 15. Exemple de modèle de registre de taille quelconque utilisant des signaux d'interface

non contraints.

entity reg is

generic (width: positive := 4);

port (clk, rst: in bit;

d: in bit_vector(width-1 downto 0);

q: out bit_vector(width-1 downto 0));

end entity reg;

```

signal data, data\_reg: bit\_vector(databus\_size-1 downto 0);

Code 16. Modèle plus robuste quant aux tailles des signaux.

port map (data, data\_reg);

regA: entity WORK.reg(bhv)

constant databus\_size: positive := 16;

generic map (width => databus size)

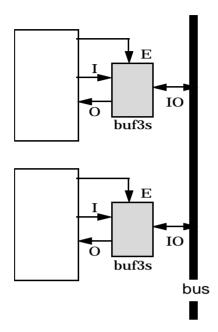

### Objets d'interface non contraints

Le Code 15 illustre l'exemple du modèle d'un registre de taille quelconque dont les signaux d'interfaces sont déclarés comme des tableaux non contraints. La déclaration d'entité possède une partie d'instruction qui vérifie que les tailles des signaux D et Q sont les mêmes, sinon il y aura une erreur au moment où une instance du composant tentera d'assigner la valeur du signal D au signal Q. L'avantage de mettre ce test dans la déclaration d'entité est de le rendre effectif quelle que soit l'architecture utilisée.

Le corps d'architecture définit un reset asynchrone. Dès que le signal RST est actif, le registre est mis à zéro. La taille de la constante ZERO est paramétrée en fonction de la taille du signal Q. Noter l'usage de l'agrégat avec le mot clé **others** pour initialiser la constante sans devoir connaître sa taille exacte.

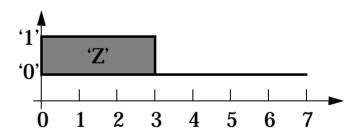

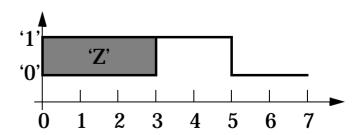

Une instance du composant REG doit nécessairement spécifier les tailles des ports effectifs. Les déclarations des signaux associés aux ports fixent automatiquement ces tailles. Si les tailles ne sont pas les mêmes dans ce cas, une erreur sera reportée par le modèle.